Voir la traduction automatique

Ceci est une traduction automatique. Pour voir le texte original en anglais cliquez ici

#IT & technologies - Telecom

{{{sourceTextContent.title}}}

Les morceaux élevés évitent des limitations conventionnelles d'IC

{{{sourceTextContent.subTitle}}}

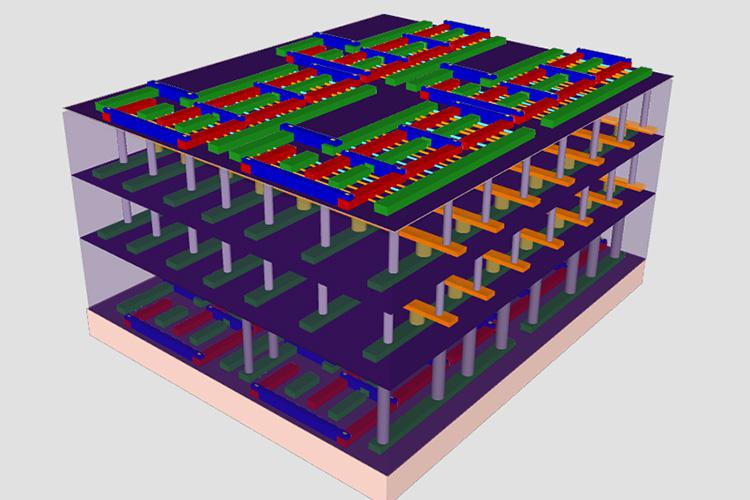

Les ingénieurs de Stanford ont créé un morceau four-layer de high-rise de prototype. Dans cette image, le fond et les couches supérieures sont des transistors de logique faits de nanotubes de carbone. Serrées entre eux sont deux couches de la mémoire à accès sélectif résistive (RRAM). Les tubes verticaux sont des « ascenseurs » électroniques de nanoscale qui relient la logique et la mémoire, les laissant fonctionner ensemble

{{{sourceTextContent.description}}}

Une équipe de technologie à l'Université de Stanford a trouvé un moyen d'améliorer des puces en les rendant plus grandes. Selon l'équipe, les morceaux courants souffrent de ? fils bloqués " quand les composants de logique et de mémoire deviennent surchargés. Leur solution--ajoutant des couches de logique placé sur la mémoire et employer le nanoscale électronique ? ascenseurs ? pour déplacer des données entre les couches--élimine des goulots créés par des fils et déplace de ce fait des données plus rapidement utilisant moins d'électricité.

Il a fallu à l'équipe trois percées pour pouvoir établir un prototype four-story de leur morceau élevé. Le premier construisait efficacement les transistors de carbone-nanotube de nanoscale (CNTs) qui pourraient plus complètement être scellés que les transistors conventionnels courants--quels électrons de fuite, créant la chaleur et gaspillant l'électricité. Jusqu'ici, CNTs n'a pas pu être développé ensemble étroitement. Pour venir à bout cette limitation, les ingénieurs de Stanford ont élevé CNTs sur une gaufrette de quartz et ont puis employé un de film métallique qui agit comme le ruban adhésif de les soulever outre du quartz et de les transférer à une gaufrette de silicium. Après que 12 transferts plus semblables, ils aient assemblé un de la rangée la plus dense de CNTs jamais faite, puis l'a employée comme base de leur morceau élevé. Il ? le notable de s que l'équipe pourrait faire ceci avec l'équipement de laboratoire plutôt que la vitesse sophistiquée a employé aux installations de fabrication commerciales. D'ailleurs, elles ont montré que cette technique pourrait établir plus d'une couche de logique CNTs.

L'équipe de Stanford a également proposé une méthode d'établir un nouveau type de mémoire directement sur la couche de CNT. La mémoire est un sandwich à métal-oxyde-métal de la nitrure, de l'oxyde d'hafnium, et du platine titaniques--il n'y a aucun silicium. Ce sandwich résiste à l'écoulement courant dans une direction et le permet dans la direction opposée. Le changement de résistif aux états conducteurs laisse cette nouvelle mémoire --une mémoire à accès sélectif ou un RRAM résistive--créez les zéros numériques et ceux. La nouvelle mémoire emploie moins d'électricité que la mémoire conventionnelle de silicium et peut être construite à de plus basses températures, ainsi elle est compatible avec les processus de fabrication et les matériaux élevés.

La percée finale était des milliers de perçage d'interconnexions (ascenseurs de signal de nanoscale) par les couches de mémoire aux couches de CNTs au-dessous de elles. Tout ceux relie ensemble éliminent les embouteillages des signaux communs sur les cartes à circuits conventionnelles. Il n'y a aucune manière comparable d'ajouter des interconnexions entre la mémoire et la logique silicium-basées sur les morceaux conventionnels construits comme high-rises. Cela ? s parce qu'il prend les températures aussi hautes que 1,000°C pour créer la mémoire de silicium, et celui fondraient tous les composants de logique ci-dessous.